# mos integrated circuit $\mu$ PD77210, 77213

# **16-BIT FIXED-POINT DIGITAL SIGNAL PROCESSOR**

The  $\mu$ PD77210 and 77213 are 16-bit fixed-point digital signal processors (DSP).

Compared with the existing members of the  $\mu$ PD77111 Family, the  $\mu$ PD77210 Family consumes less power and is ideal for battery-driven mobile terminal applications such as PDAs and cellular telephones. The  $\mu$ P77210 Family is DSP is also compatible with the  $\mu$ PD77111 Family at the binary level.

The  $\mu$ PD77210 Family consists of the  $\mu$ PD77210 and 77213. Unless otherwise specified, the  $\mu$ PD77210 Family refers to the entire family. If there are some differences in function or operation among family products, they are described under their respective names.

The functions of the  $\mu$ PD77210 Family are described in detail in the following user's manuals. Refer to these manuals when designing your system.

μPD77210 Family User's Manual - Architecture: μPD77016 Family User's Manual - Instructions: In preparation U13116E

# **FEATURES**

NEC

• Instruction cycle (operating clock):

μPD77210 6.25 ns MIN. (160 MHz MAX.) μPD77213 8.33 ns MIN. (120 MHz MAX.)

# Memory

-Internal instruction memory:

$\mu$ PD77210 :RAM 31.5 Kwords x 32 bits  $\mu$ PD77213 :RAM 15.5 Kwords x 32 bits ROM 64 Kwords x 32 bits

-Data memory:

μPD77210 :RAM 30 Kwords x 16 bits x 2 planes (X and Y data memories)

External memory space 1 Mwords x 16 bits (common to X and Y data memories)

μPD77213 :RAM 18 Kwords x 16 bits x 2 planes (X and Y data memories)

ROM 32 Kwords x 16 bits x 2 planes (X and Y data memories)

External memory space 1 Mwords x 16 bits (common to X and Y data memories)

Peripheral

| -Audio serial interface: 1 channel         | -16-bit timer: 2 channels                |

|--------------------------------------------|------------------------------------------|

| -Time-division serial interface: 1 channel | -Peripheral-memory DMA transfer function |

| -16-bit host interface: 1 channel          | -SD (Secure Digital) card interface      |

| -16-bit general-purpose port               | :µPD77213 only                           |

|                                            |                                          |

The information in this document is subject to change without notice. Before using this document, please confirm that this is the latest version. Not all devices/types available in every country. Please check with local NEC representative for availability and additional information.

# Supply voltage

| -DSP core supply voltage: | 1.425 to 1.65 V (MAX. operating speed 120 MHz),                        |

|---------------------------|------------------------------------------------------------------------|

|                           | 1.55 to 1.65 V (MAX. operating speed 160 MHz) $\mu\text{PD77210}$ only |

| -I/O pin supply voltage:  | 2.7 to 3.6 V                                                           |

# ORDERING INFORMATION

| Parts Number       | Package                                     |

|--------------------|---------------------------------------------|

| μPD77210F1-DA2     | 161-pin plastic fine pitch BGA (10 x 10)    |

| μPD77210GJ-8EN     | 144-pin plastic LQFP (fine pitch) (20 x 20) |

| μPD77213F1-xxx-DA2 | 161-pin plastic fine pitch BGA (10 x 10)    |

| μPD77213GJ-xxx-8EN | 144-pin plastic LQFP (fine pitch) (20 x 20) |

Remark xxx indicates ROM code suffix.

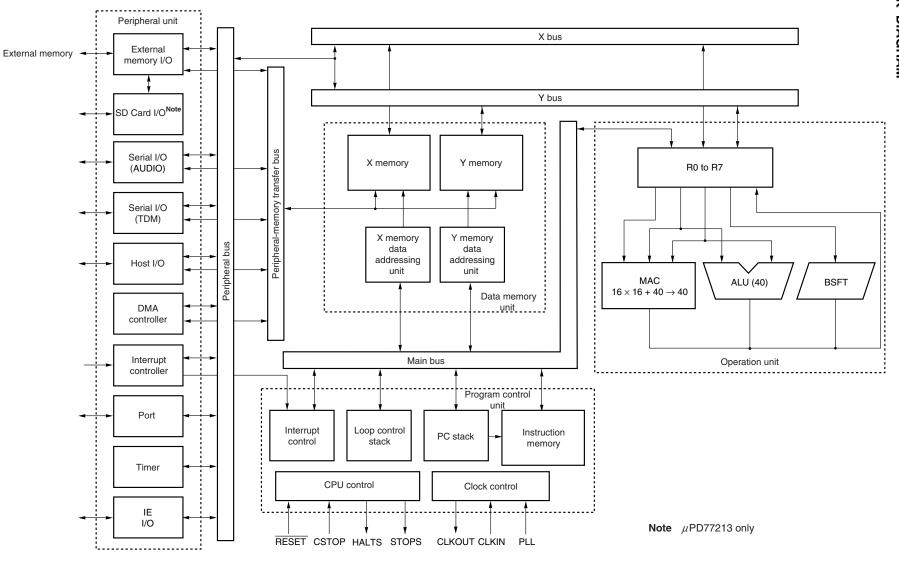

BLOCK DIAGRAM

Z

μPD77210, 77213

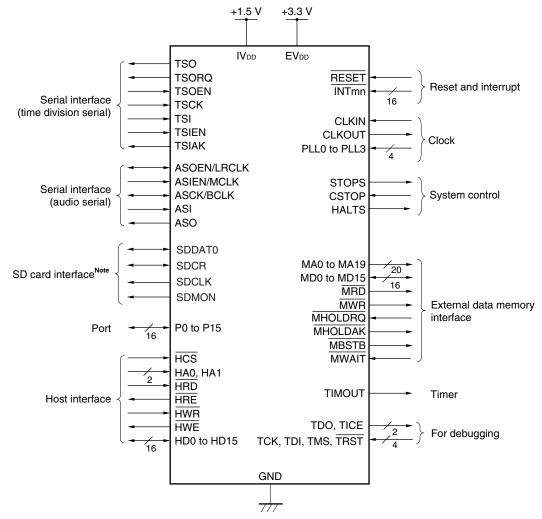

# FUNCTIONAL PIN BLOCK

Note µPD77213 only

Caution Some port pins, host interface pins, serial interface pins, interrupt pins, and SD card interface pins are alternate function pins.

**Remark** m, n = 0 to 3

| Ζ |

|---|

| П |

|   |

# DSP FUNCTION LIST

|                                                | Item                                          | μPD77110                                         | μPD77111                                      | μPD77112                     | μPD77113A           | μPD77114                             | μPD77115                                          | μPD77210                                        | μPD77213                                        |  |

|------------------------------------------------|-----------------------------------------------|--------------------------------------------------|-----------------------------------------------|------------------------------|---------------------|--------------------------------------|---------------------------------------------------|-------------------------------------------------|-------------------------------------------------|--|

| Memory                                         | Int. instruction RAM                          | 35.5 K × 32                                      | 1 K × 32                                      |                              | 3.5 K × 32          |                                      | 11.5 K × 32                                       | 31.5 K × 32                                     | 15.5 K × 32                                     |  |

| space                                          | Int. instruction ROM                          | None                                             | 31.75                                         | K × 32                       | 48 K × 32           |                                      | None                                              |                                                 | 64K × 32                                        |  |

| (words ×<br>bits)                              | Data RAM<br>(X/Y memory)                      | 24 K $	imes$ 16 each                             | <b>3 K</b> × 1                                | 16 each                      | 16 K × 16 each      |                                      | 16 K × 16 each                                    | 30 K × 16 each                                  | 18 K × 16 each                                  |  |

|                                                | Data ROM<br>(X/Y memory)                      | None                                             | 16 K ×                                        | 16 each                      | 32 K × 16 each      |                                      | None                                              |                                                 | $32 \text{ K} \times 16 \text{ each}$           |  |

|                                                | Ext. instruction memory                       |                                                  |                                               |                              | No                  | ne                                   | 1                                                 |                                                 | I                                               |  |

|                                                | Ext. data memory (X/Y<br>memory)              | 32  K 	imes 16  each                             | None                                          | 16 K × 16 each               | None                | $8 \text{ K} \times 16 \text{ each}$ | None                                              | 1 M×16                                          | 1 M $\times$ 16 (8 K $\times$ 16, using SD I/F) |  |

| Instruction cycle (at maximum operating speed) |                                               | 15.3 ns<br>(65 MHz)                              |                                               |                              | 13.3 ns<br>(75 MHz) |                                      | 6.25 ns<br>(160 MHz)                              | 8.33 ns<br>(120 MHz)                            |                                                 |  |

| Multiple                                       |                                               | Integer multiple<br>of ×1 to 8<br>(external pin) | Integer multiple of ×1 to 16<br>(mask option) |                              |                     |                                      | Integer multiple<br>of ×1 to 16<br>(external pin) | Integer multiple of ×10 to 64<br>(external pin) |                                                 |  |

| Peripheral                                     | Serial interface                              |                                                  |                                               | 2 channels<br>(speech CODEC) |                     | 1 channel<br>(audio CODEC)           | 2 channels (time-division, audio)                 |                                                 |                                                 |  |

|                                                | Host interface                                |                                                  | 8-bit bus                                     |                              |                     |                                      |                                                   | 16-bit bus                                      |                                                 |  |

|                                                | General-purpose<br>port (I/O<br>programmable) |                                                  |                                               | 4 bits                       |                     | 8 bits                               | 16 bits (some are alternative with host)          |                                                 |                                                 |  |

|                                                | Timer                                         |                                                  |                                               | None (1                      |                     |                                      | 1 channel<br>(16-bit resolution)                  | 2 channels<br>(16-bit resolution)               |                                                 |  |

|                                                | Others                                        | -                                                | -                                             | -                            | -                   | _                                    | SD card I/F                                       | -                                               | SD card I/F                                     |  |

| Supply voltage                                 |                                               |                                                  | DSP core: 2.5 V<br>I/O pins: 3 V              |                              |                     |                                      |                                                   | DSP core: 1.5 V<br>I/O pins: 3.3 V              |                                                 |  |

| Package                                        |                                               | 100-pin TQFP                                     | 80-pin TQFP<br>80-pin FBGA                    | 100-pin TQFP                 | 80-pin FBGA         | 100-pin TQFP                         | 80-pin TQFP<br>80-pin FBGA                        |                                                 | n FBGA<br>n LQFP                                |  |

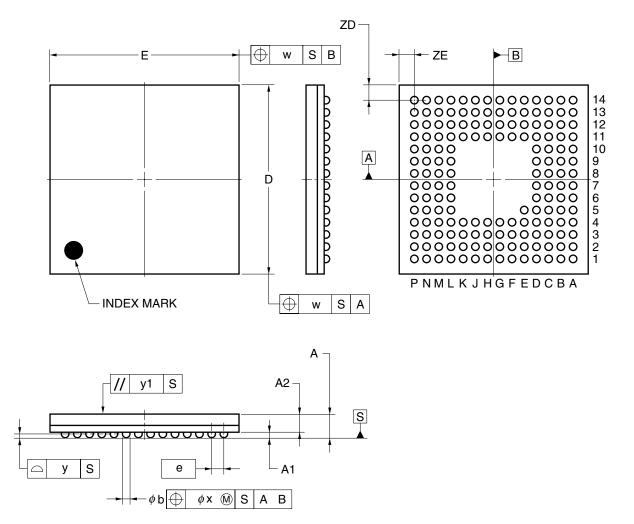

# **PIN CONFIGURATIONS**

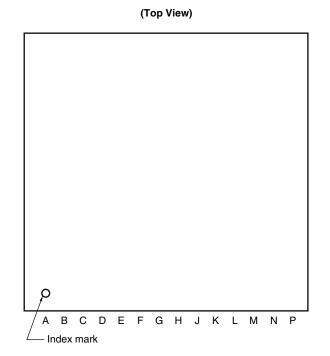

161-pin plastic fine pitch BGA (10 x 10) •μPD77210F1-DA2 •μPD77213F1-xxx-DA2

(Bottom View)

| 000000000000000000000000000000000000000 | 14<br>13 |

|-----------------------------------------|----------|

|                                         | 13       |

|                                         | 10       |

| 0000000000000000                        | 12       |

| 000000000000000                         | 11       |

| 0000 0000                               | 10       |

| 0000 0000                               | 9        |

| 0000 0000                               | 8        |

| 0000 0000                               | 7        |

| 0000 0000                               | 6        |

| 0000 00000                              | 5        |

| 000000000000000                         | 4        |

| 000000000000000                         | 3        |

| 000000000000000                         | 2        |

| 00000000000000                          | 1        |

| P N M L K J H G F E D C B A             | I        |

| Pin No. | Pin Name     | Pin No. | Pin Name       | Pin No. | Pin Name                    | Pin No. | Pin Name                      |

|---------|--------------|---------|----------------|---------|-----------------------------|---------|-------------------------------|

| A1      | NC           | C14     | EVDD           | H2      | HD7                         | M5      | TSORQ                         |

| A2      | NC           | D1      | P10/HD10/INT22 | H3      | HD6                         | M6      | MA0                           |

| A3      | P5/INT11     | D2      | P11/HD11/INT32 | H4      | GND                         | M7      | MA4                           |

| A4      | P2/INT20     | D3      | P12/HD12/INT03 | H11     | MD5                         | M8      | MA5                           |

| A5      | GND          | D4      | GND            | H12     | MD4                         | M9      | MA10                          |

| A6      | EVDD         | D5      | GND            | H13     | MD1                         | M10     | MA12                          |

| A7      | IVdd         | D6      | P1/INT10       | H14     | MD3                         | M11     | MA15/Reserved <sup>Note</sup> |

| A8      | IVdd         | D7      | GND            | J1      | EVDD                        | M12     | MA19/SDCLK <sup>Note</sup>    |

| A9      | PLL0         | D8      | GND            | J2      | HCS                         | M13     | MA18/SDCR <sup>Note</sup>     |

| A10     | STOPS        | D9      | GND            | J3      | HA1                         | M14     | EVDD                          |

| A11     | EVDD         | D10     | GND            | J4      | HWR                         | N1      | NC                            |

| A12     | TRST         | D11     | TMS            | J11     | GND                         | N2      | NC                            |

| A13     | NC           | D12     | TICE           | J12     | MD0                         | N3      | ASIEN/MCLK                    |

| A14     | NC           | D13     | MD12           | J13     | MBSTB                       | N4      | TSCK                          |

| B1      | NC           | D14     | MD15           | J14     | IVDD                        | N5      | TSIAK                         |

| B2      | NC           | E1      | P14/HD14/INT23 | K1      | HA0                         | N6      | MA1                           |

| B3      | P7/INT31     | E2      | P15/HD15/INT33 | K2      | HRD                         | N7      | MA2                           |

| B4      | P6/INT21     | E3      | P13/HD13/INT13 | К3      | TIMOUT                      | N8      | MA7                           |

| B5      | P3/INT30     | E4      | GND            | K4      | ASO                         | N9      | MA9                           |

| B6      | CLKOUT       | E5      | NC             | K11     | GND                         | N10     | MA11                          |

| B7      | IVdd         | E11     | GND            | K12     | MWR                         | N11     | MA16/Reserved <sup>Note</sup> |

| B8      | PLL3         | E12     | MD14           | K13     | MWAIT                       | N12     | MA17/Reserved <sup>Note</sup> |

| B9      | PLL1         | E13     | MD9            | K14     | EVDD                        | N13     | NC                            |

| B10     | CSTOP        | E14     | MD11           | L1      | HWE                         | N14     | NC                            |

| B11     | I.C.         | F1      | EVDD           | L2      | HRE                         | P1      | NC                            |

| B12     | тск          | F2      | HD1            | L3      | GND                         | P2      | NC                            |

| B13     | NC           | F3      | HD2            | L4      | GND                         | P3      | ASI                           |

| B14     | NC           | F4      | HD0            | L5      | TSIEN                       | P4      | TSO                           |

| C1      | EVDD         | F11     | MD10           | L6      | GND                         | P5      | TSI                           |

| C2      | P8/HD8/INT02 | F12     | MD13           | L7      | GND                         | P6      | EVDD                          |

| C3      | P9/HD9/INT12 | F13     | MD7            | L8      | MA8                         | P7      | IVdd                          |

| C4      | P4/INT01     | F14     | EVDD           | L9      | GND                         | P8      | МАЗ                           |

| C5      | P0/INT00     | G1      | HD3            | L10     | MA14/SDDAT0 <sup>Note</sup> | P9      | MA6                           |

| C6      | CLKIN        | G2      | HD5            | L11     | GND                         | P10     | EVDD                          |

| C7      | PLL2         | G3      | HD4            | L12     | MHOLDRQ                     | P11     | MA13/SDMON <sup>Note</sup>    |

| C8      | HALTS        | G4      | GND            | L13     | MRD                         | P12     | EVDD                          |

| C9      | RESET        | G11     | GND            | L14     | MHOLDAK                     | P13     | NC                            |

| C10     | I.C.         | G12     | MD8            | M1      | EVDD                        | P14     | NC                            |

| C11     | TDI          | G13     | MD2            | M2      | ASCK/BCLK                   |         |                               |

| C12     | TDO          | G14     | MD6            | M3      | ASOEN/LRCLK                 |         |                               |

| C13     | GND          | H1      | IVDD           | M4      | TSOEN                       |         |                               |

**Note** MA13 to MA19 pins of the  $\mu$ PD77213 are alternate function pins.

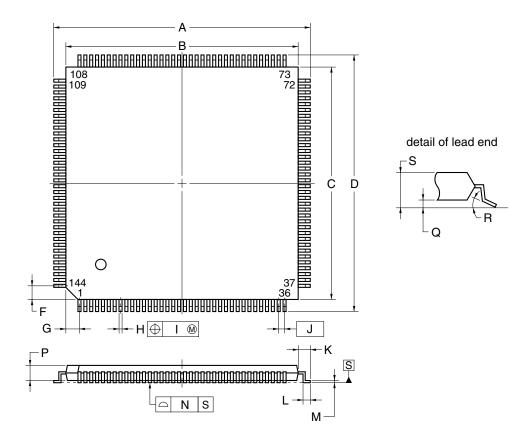

NEC

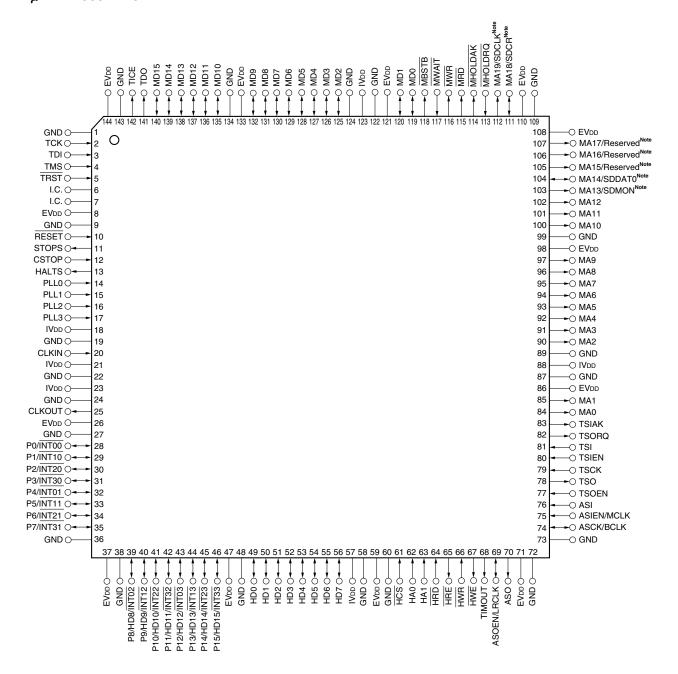

144-pin plastic LQFP (fine pitch) (20 x 20) (Top View) •μPD77210GJ-8EN •μPD77213GJ-xxx-8EN

| Pin No. | Pin Name | Pin No. | Pin Name       | Pin No. | Pin Name                      | Pin No. | Pin Name                   |

|---------|----------|---------|----------------|---------|-------------------------------|---------|----------------------------|

| 1       | GND      | 37      | EVDD           | 73      | GND                           | 109     | GND                        |

| 2       | тск      | 38      | GND            | 74      | ASCK/BCLK                     | 110     | EVDD                       |

| 3       | TDI      | 39      | P8/HD8/INT02   | 75      | ASIEN/MCLK                    | 111     | MA18/SDCR <sup>Note</sup>  |

| 4       | TMS      | 40      | P9/HD9/INT12   | 76      | ASI                           | 112     | MA19/SDCLK <sup>Note</sup> |

| 5       | TRST     | 41      | P10/HD10/INT22 | 77      | TSOEN                         | 113     | MHOLDRQ                    |

| 6       | I.C.     | 42      | P11/HD11/INT32 | 78      | TSO                           | 114     | MHOLDAK                    |

| 7       | I.C.     | 43      | P12/HD12/INT03 | 79      | тэск                          | 115     | MRD                        |

| 8       | EVDD     | 44      | P13/HD13/INT13 | 80      | TSIEN                         | 116     | MWR                        |

| 9       | GND      | 45      | P14/HD14/INT23 | 81      | TSI                           | 117     | MWAIT                      |

| 10      | RESET    | 46      | P15/HD15/INT33 | 82      | TSORQ                         | 118     | MBSTB                      |

| 11      | STOPS    | 47      | EVDD           | 83      | TSIAK                         | 119     | MD0                        |

| 12      | CSTOP    | 48      | GND            | 84      | MA0                           | 120     | MD1                        |

| 13      | HALTS    | 49      | HD0            | 85      | MA1                           | 121     | EVDD                       |

| 14      | PLL0     | 50      | HD1            | 86      | EVDD                          | 122     | GND                        |

| 15      | PLL1     | 51      | HD2            | 87      | GND                           | 123     | IVdd                       |

| 16      | PLL2     | 52      | HD3            | 88      | IVdd                          | 124     | GND                        |

| 17      | PLL3     | 53      | HD4            | 89      | GND                           | 125     | MD2                        |

| 18      | IVdd     | 54      | HD5            | 90      | MA2                           | 126     | MD3                        |

| 19      | GND      | 55      | HD6            | 91      | MA3                           | 127     | MD4                        |

| 20      | CLKIN    | 56      | HD7            | 92      | MA4                           | 128     | MD5                        |

| 21      | IVdd     | 57      | IVDD           | 93      | MA5                           | 129     | MD6                        |

| 22      | GND      | 58      | GND            | 94      | MA6                           | 130     | MD7                        |

| 23      | IVdd     | 59      | EVDD           | 95      | MA7                           | 131     | MD8                        |

| 24      | GND      | 60      | GND            | 96      | MA8                           | 132     | MD9                        |

| 25      | CLKOUT   | 61      | HCS            | 97      | MA9                           | 133     | EVDD                       |

| 26      | EVDD     | 62      | HA0            | 98      | EVDD                          | 134     | GND                        |

| 27      | GND      | 63      | HA1            | 99      | GND                           | 135     | MD10                       |

| 28      | P0/INT00 | 64      | HRD            | 100     | MA10                          | 136     | MD11                       |

| 29      | P1/INT10 | 65      | HRE            | 101     | MA11                          | 137     | MD12                       |

| 30      | P2/INT20 | 66      | HWR            | 102     | MA12                          | 138     | MD13                       |

| 31      | P3/INT30 | 67      | HWE            | 103     | MA13/SDMON <sup>Note</sup>    | 139     | MD14                       |

| 32      | P4/INT01 | 68      | TIMOUT         | 104     | MA14/SDDAT0 <sup>Note</sup>   | 140     | MD15                       |

| 33      | P5/INT11 | 69      | ASOEN/LRCLK    | 105     | MA15/Reserved <sup>Note</sup> | 141     | TDO                        |

| 34      | P6/INT21 | 70      | ASO            | 106     | MA16/Reserved <sup>Note</sup> | 142     | TICE                       |

| 35      | P7/INT31 | 71      | EVDD           | 107     | MA17/Reserved <sup>Note</sup> | 143     | GND                        |

| 36      | GND      | 72      | GND            | 108     | EVDD                          | 144     | EVDD                       |

**Note** MA13 to MA19 pins of the  $\mu$ PD77213 are alternate function pins.

NEC

# Pin Name

| ASCK        | :Audio Serial Clock Input/Output   | MWAIT     | :External Data Memory Access Wait          |

|-------------|------------------------------------|-----------|--------------------------------------------|

| ASI         | :Audio Serial Data Input           |           | Input                                      |

| ASIEN       | :Audio Serial Input Enable         | NC        | :Non-Connection                            |

| ASO         | :Audio Serial Data Output          | P0 to P15 | :Port                                      |

| ASOEN       | :Audio Serial Output Enable        | PLL0-PLL3 | :PLL Multiple Rate Set                     |

| BCLK        | :Bit Clock Input/Output            | Reserved  | :Reserved                                  |

| CLKIN       | :Clock Input                       | RESET     | :Reset                                     |

| CLKOUT      | :Clock Output                      | SDCLK     | :SD Card Clock Output                      |

| CSTOP       | :Clear Stop Mode                   | SDCR      | :SD Card Command Output/Response           |

| EVDD        | :Power Supply for I/O Pins         |           | Input                                      |

| GND         | :Ground                            | SDDAT0    | :SD Card Data Input/Output                 |

| HALTS       | :Halt Status Signal Output         | SDMON     | :SD Card Access Monitor                    |

| HD0 to HD15 | :Host Data Bus                     | STOPS     | :Stop Status Signal Output                 |

| HCS         | :Host Chip Select                  | ТСК       | :Test Clock Input                          |

| HA0, HA1    | :Host Data Access                  | TDI       | :Test Data Input                           |

| HRD         | :Host Read                         | TDO       | :Test Data Output                          |

| HRE         | :Host Read Enable                  | TICE      | :Test In-Circuit Emulator                  |

| HWE         | :Host Write Enable                 | TIMOUT    | :Timer Time Out Monitor Output             |

| HWR         | :Host Write                        | TMS       | :Test Mode Select                          |

| I.C.        | Internal Connection                | TRST      | :Test Reset                                |

| IVdd        | :Power Supply for DSP Core         | TSCK      | :Time Division Multiplex Serial Clock      |

| INTmn       | :Interrupt (m,n=0 to 3)            |           | Input                                      |

| LRCLK       | :Left Right Clock Input/Output     | TSI       | :Time Division Multiplex Serial Data Input |

| MA0 to MA19 | :External Data Memory Address Bus  | TSIAK     | :Time Division Multiplex Serial Input      |

| MBSTB       | :External Data Memory Bus Strobe   |           | Acknowledge                                |

| MCLK        | :Master Clock Input                | TSIEN     | :Time Division Multiplex Serial Input      |

| MD0 to MD15 | :External Data Memory Bus          |           | Enable                                     |

| MHOLDAK     | :External Data Memory Bus Hold     | TSO       | :Time Division Multiplex Serial Data       |

|             | Acknowledge                        |           | Output                                     |

| MHOLDRQ     | :External Data Memory Bus Hold     | TSOEN     | :Time Division Multiplex Serial Output     |

|             | Request                            |           | Enable                                     |

| MRD         | :External Data Memory Read Output  | TSORQ     | :Time Division Multiplex Serial Output     |

| MWR         | :External Data Memory Write Output |           | Request                                    |

|             |                                    |           |                                            |

# CONTENTS

| 1. | PIN FUNCTIONS                                                   | 13 |

|----|-----------------------------------------------------------------|----|

|    | 1.1 Description of Pin Functions                                | 13 |

|    | 1.2 Connection of Unused Pins                                   | 21 |

|    | 1.2.1 Connection of functional pins                             | 21 |

|    | 1.2.2 Connection of non-functional pin                          | 22 |

|    |                                                                 |    |

| 2. | . FUNCTIONAL OUTLINE                                            |    |

|    | 2.1 Program Control Unit                                        | 23 |

|    | 2.1.1 CPU control                                               | 23 |

|    | 2.1.2 Interrupt control                                         |    |

|    | 2.1.3 Loop control stack                                        |    |

|    | 2.1.4 PC stack                                                  |    |

|    | 2.1.5 Clock control                                             |    |

|    | 2.1.6 Instruction memory                                        |    |

|    | 2.2 Operation Unit                                              |    |

|    | 2.2.1 General-purpose registers (R0 to R7)                      |    |

|    | 2.2.2 Multiply accumulator (MAC)                                |    |

|    | 2.2.3 Arithmetic logic unit (ALU)                               |    |

|    | 2.2.4 Barrel shifter (BSFT)                                     |    |

|    | 2.3 Data Memory Unit                                            |    |

|    | 2.3.1 Data memory                                               |    |

|    | 2.3.2 Data addressing unit                                      |    |

|    | 2.4 Peripheral Unit                                             |    |

|    | 2.4.1 Serial interface (SIO)                                    |    |

|    | 2.4.2 Host interface (HIO)                                      |    |

|    | 2.4.3 General-purpose I/O port (PIO)                            |    |

|    | 2.4.4 External memory interface (MIO)                           |    |

|    | 2.4.5 Timers (TIM1 and TIM2)                                    |    |

|    | 2.4.6 Interrupt controller (INTC)<br>2.4.7 DMA controller (PMT) |    |

|    | 2.4.7 DWA controller (PMT)                                      |    |

|    |                                                                 |    |

|    | 2.4.9 Debug interface (IEIO)                                    | 20 |

| 2  | CLOCK GENERATOR                                                 | 97 |

| 0. |                                                                 |    |

| 4. | RESET FUNCTION                                                  |    |

|    | 4.1 Hardware Reset                                              |    |

|    |                                                                 | 20 |

| 5. | FUNCTION OF BOOT-UP ROM                                         |    |

|    | 5.1 Boot at Reset                                               | -  |

|    | 5.1.1 Memory boot                                               |    |

|    | 5.1.2 Host boot                                                 |    |

|    | 5.1.3 Serial boot                                               |    |

|    | 5.2 Reboot                                                      |    |

|    | 5.2.1 Memory reboot                                             |    |

# NEC

| 5.2.2 Host reboot                     |    |

|---------------------------------------|----|

| 5.2.3 Serial reboot                   |    |

|                                       |    |

| 6. STANDBY MODE                       |    |

| 6.1 Halt Mode                         |    |

| 6.2 Stop Mode                         |    |

| 7. MEMORY MAP                         |    |

| 7.1 Instruction Memory                |    |

| 7.1.1 Instruction memory map          |    |

| 7.1.2 Interrupt vector table          |    |

| 7.2 Data Memory                       |    |

| 7.2.1 Data memory map                 |    |

| 7.2.2 Internal peripherals            |    |

|                                       |    |

| 8. GENERAL-PURPOSE PORT AND INTERRUPT |    |

| 8.1 General-purpose Port Pins         |    |

| 8.2 Interrupt Pin                     |    |

| 9. INSTRUCTION                        | 39 |

| 9.1 Outline of Instruction            |    |

| 9.2 Instruction Set and Its Operation |    |

|                                       |    |

| 10. ELECTRICAL SPECIFICATIONS         |    |

|                                       |    |

| 11. PACKAGE DRAWINGS                  |    |

|                                       |    |

# **1. PIN FUNCTIONS**

Because the pin numbers differ depending on the package, see the column for the package to be used in the tables below.

# 1.1 Description of Pin Functions

#### • Power supply pins

| Pin Name         | Pin No.                                                                               |                                                                                           | I/O | Function                                                                                    | Alternate |

|------------------|---------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|-----|---------------------------------------------------------------------------------------------|-----------|

|                  | 144-pin LQFP                                                                          | 161-pin FBGA                                                                              |     |                                                                                             | Pin       |

| IVdd             | 18,21,23,57,<br>88,123                                                                | A7,A8,B7,H1,<br>J14, P7                                                                   | _   | Power supply for DSP core (+1.5 V)<br>These pins supply power to the DSP core.              | -         |

| EV <sub>DD</sub> | 8,26,37,47,59,<br>71,86,98,108,<br>110,121,133,<br>144                                | A6,A11,C1,<br>C14,F1,F14,<br>J1,K14,M1,<br>M14,P6,P10,<br>P12                             | _   | Power supply for I/O (+3.3 V)<br>These pins supply power to the external interface<br>pins. | _         |

| GND              | 1,9,19,22,24,<br>27,36,38,48,<br>58,60,72,73,<br>87,89,99,109,<br>122,124,134,<br>143 | A5,C13,D4,D5,<br>D7,D8,D9,D10,<br>E4,E11,G4,<br>G11,H4,J11,<br>K11,L3,L4,L6,<br>L7,L9,L11 | _   | Ground<br>These are ground pins.                                                            | _         |

**Remark** Please supply voltage to the  $IV_{DD}$  and  $EV_{DD}$  pins simultaneously.

# Clock and system control pins

| Pin Name        | Pin          | No.          | I/O    | Function                                                                                                                                                                                                                                                                                                                                                                                                                  | Alternate |

|-----------------|--------------|--------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

|                 | 144-pin LQFP | 161-pin FBGA |        |                                                                                                                                                                                                                                                                                                                                                                                                                           | Pin       |

| CLKIN           | 20           | C6           | Input  | Clock input<br>This pin inputs a clock to operate the $\mu$ PD77210<br>Family.                                                                                                                                                                                                                                                                                                                                            | _         |

| CLKOUT          | 25           | B6           | Output | Internal system clock output<br>This pin outputs the internal system clock that is the<br>clock input from CLKIN and which is multiplied by the<br>PLL circuit.                                                                                                                                                                                                                                                           | _         |

| PLL0 to<br>PLL3 | 14 to 17     | A9,B9,C7,B8  | Input  | PLL multiple setting input         These pins set a clock multiple of the PLL circuit.         • PLL3: PLL2: PLL1: PLL0         0000: x10       0001: x12       0010: x14         0011: x16       0100: x18       0101: x20         0110: x22       0111: x24       1000: x26         1001: x28       1010: x30       1011: x32         1100: x40       1101: x48       1110: x56         1111: x64       1000       1000 | Ι         |

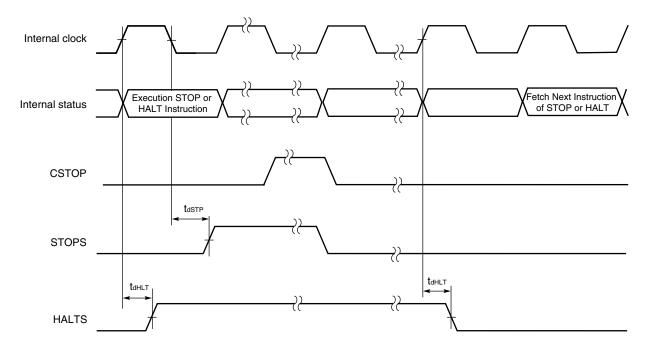

| HALTS           | 13           | C8           | Output | HALT mode status output<br>This pin is asserted active in halt mode and stop<br>mode.                                                                                                                                                                                                                                                                                                                                     | -         |

| STOPS           | 11           | A10          | Output | Stop mode status output<br>This pin is asserted active in stop mode.                                                                                                                                                                                                                                                                                                                                                      | -         |

| CSTOP           | 12           | B10          | Input  | Stop mode clear signal input<br>Stop mode is cleared when this pin is asserted<br>active.                                                                                                                                                                                                                                                                                                                                 | -         |

# • Reset and interrupt pins

| Pin Name | Pin          | No.          | I/O   | Function                                                                             | Alternate |

|----------|--------------|--------------|-------|--------------------------------------------------------------------------------------|-----------|

|          | 144-pin LQFP | 161-pin FBGA |       |                                                                                      | Pin       |

| RESET    | 10           | C9           | Input | Internal system reset signal input<br>This pin initializes the $\mu$ PD77210 Family. | _         |

| INT00    | 28           | C5           | Input | Maskable external interrupt input                                                    | P0        |

| INT01    | 32           | C4           | Input | These pins input external interrupts.                                                | P4        |

| INT02    | 39           | C2           | Input |                                                                                      | P8/HD8    |

| INT03    | 43           | D3           | Input |                                                                                      | P12/HD12  |

| INT10    | 29           | D6           | Input |                                                                                      | P1        |

| INT11    | 33           | A3           | Input |                                                                                      | P5        |

| INT12    | 40           | СЗ           | Input |                                                                                      | P9/HD9    |

| INT13    | 44           | E3           | Input |                                                                                      | P13/HD13  |

| INT20    | 30           | A4           | Input |                                                                                      | P2        |

| INT21    | 34           | B4           | Input |                                                                                      | P6        |

| INT22    | 41           | D1           | Input |                                                                                      | P10/HD10  |

| INT23    | 45           | E1           | Input |                                                                                      | P14/HD14  |

| INT30    | 31           | B5           | Input |                                                                                      | P3        |

| INT31    | 35           | В3           | Input |                                                                                      | P7        |

| INT32    | 42           | D2           | Input |                                                                                      | P11/HD11  |

| INT33    | 46           | E2           | Input |                                                                                      | P15/HD15  |

#### • External data memory interface

| Pin Name                       | Pin                                             | Pin No.                                                                                  |                | Function                                                                                                                                                                                                                   | Alternate                           |

|--------------------------------|-------------------------------------------------|------------------------------------------------------------------------------------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|

|                                | 144-pin LQFP                                    | 161-pin FBGA                                                                             |                |                                                                                                                                                                                                                            | Pin                                 |

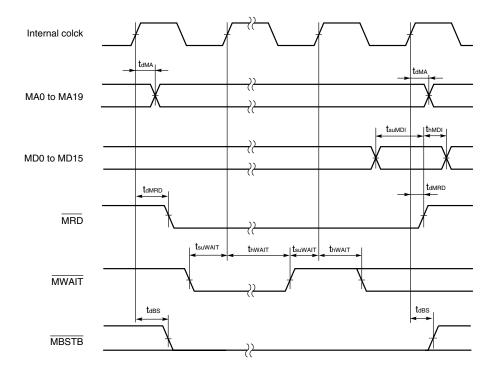

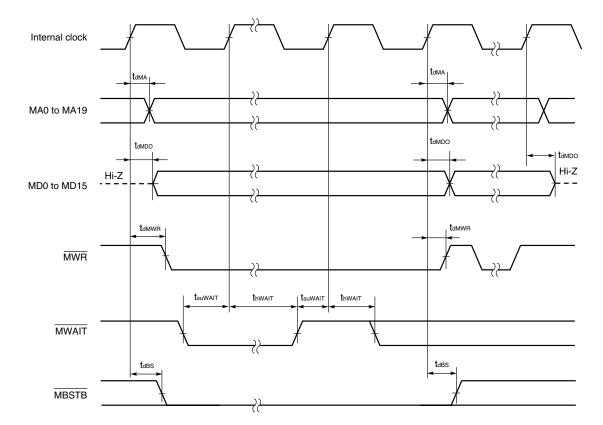

| MA0 to<br>MA19 <sup>Note</sup> | 84, 85,<br>90 to 97,<br>100 to 107,<br>111, 112 | M6,N6,N7,P8,<br>M7,M8,P9,N8,<br>L8,N9,M9,N10,<br>M10,P11,L10,<br>M11,N11,N12,<br>M13,M12 | Output<br>(3S) | Address bus of external data memory<br>These pins output an address when the external data<br>memory is accessed.                                                                                                          | SDCLK,<br>SDCR,<br>SDDAT0,<br>SDMON |

| MD0 to<br>MD15                 | 119,120,<br>125 to 132,<br>135 to 140           | J12,H13,G13,<br>H14,H12,H11,<br>G14,F13,G12,<br>E13,F11,E14,<br>D13,F12,E12,<br>D14      | I/O<br>(3S)    | 16-bit data bus<br>These pins input/output data when the external data<br>memory is accessed.                                                                                                                              | _                                   |

| MWR                            | 116                                             | К12                                                                                      | Output<br>(3S) | Write output<br>This pin outputs a write strobe signal for the external<br>data memory.                                                                                                                                    | -                                   |

| MRD                            | 115                                             | L13                                                                                      | Output<br>(3S) | Read output<br>This pin outputs a read strobe signal for the external<br>data memory.                                                                                                                                      | _                                   |

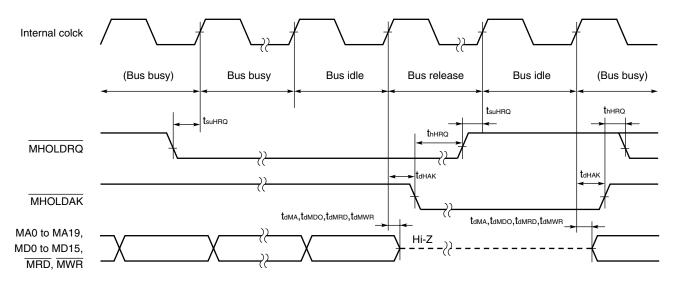

| MHOLDAK                        | 114                                             | L14                                                                                      | Output         | Hold acknowledge signal<br>This pin goes low when the external device is<br>granted use of the external data memory bus of the<br>μPD77210 Family.                                                                         | -                                   |

| MHOLDRQ                        | 113                                             | L12                                                                                      | Input          | Hold request signal<br>The external device inputs a low level to this pin<br>when it uses the external data memory bus of the<br>$\mu$ PD77210 Family.                                                                     | _                                   |

| MWAIT                          | 117                                             | К13                                                                                      | Input          | <ul> <li>Wait signal input</li> <li>This pin inserts wait cycles when the μPD77210</li> <li>Family accesses the external data memory.</li> <li>0: Inserts wait cycles.</li> <li>1: Does not insert wait cycles.</li> </ul> | _                                   |

| MBSTB                          | 118                                             | J13                                                                                      | Output         | Bus strobe signal<br>This pin goes low while the $\mu$ PD77210 Family uses<br>the external data memory bus.                                                                                                                | _                                   |

Note MA13 to MA19 pins of the  $\mu$ PD77213 are alternate function pins.

**Remark** Those pins marked "3S" in the above table enter the high-impedance state under the following conditions:

MA0 to MA19, MRD, and MWR: When the bus is released (MHOLDAK = low level)

MD0 to MD15: When the external data memory is not accessed and when the bus is released  $(\overline{MHOLDAK} = low level)$

• Timer

| Pin Name | Pin No.      |              | I/O    | Function                                                                  | Alternate |

|----------|--------------|--------------|--------|---------------------------------------------------------------------------|-----------|

|          | 144-pin LQFP | 161-pin FBGA |        |                                                                           | Pin       |

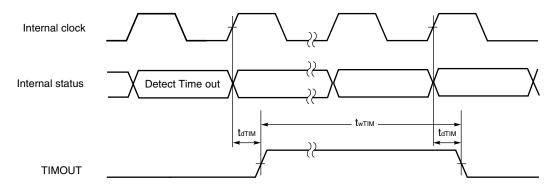

| TIMOUT   | 68           | КЗ           | Output | Time out monitor<br>This pin is asserted active when the timer times out. | -         |

# Serial interface

| Pin Name | Pir          | No.          | I/O    | Function                                                 | Alternate |

|----------|--------------|--------------|--------|----------------------------------------------------------|-----------|

|          | 144-pin LQFP | 161-pin FBGA |        |                                                          | Pin       |

| ASCK/    | 74           | M2           | I/O    | Audio serial clock input/output                          | -         |

| BCLK     |              |              |        | ASCK:Audio serial clock input                            |           |

|          |              |              |        | BCLK:Serial clock I/O                                    |           |

| ASO      | 70           | К4           | Output | Audio serial data output                                 | -         |

|          |              |              | (3S)   |                                                          |           |

| ASI      | 76           | P3           | Input  | Audio serial data input                                  | _         |

| ASOEN/   | 69           | МЗ           | I/O    | Audio serial output enable/left right clock input output | -         |

| LRCLK    |              |              |        | ASOEN: Audio serial output enable input                  |           |

|          |              |              |        | LRCLK:Left right clock I/O                               |           |

| ASIEN/   | 75           | N3           | Input  | Audio serial input enable/master clock input output      | -         |

| MCLK     |              |              |        | ASIEN:Audio serial input enable input                    |           |

|          |              |              |        | MCLK:Master clock input (in master mode)                 |           |

| TSCK     | 79           | N4           | Input  | Clock input for time division serial                     | -         |

| TSO      | 78           | P4           | Output | Time-division serial data output                         | -         |

|          |              |              | (3S)   |                                                          |           |

| TSI      | 81           | P5           | Input  | Time-division serial data input                          | -         |

| TSORQ    | 82           | M5           | Output | Time-division serial output request                      | _         |

| TSOEN    | 77           | M4           | Input  | Time-division serial output enable                       | _         |

| TSIEN    | 80           | L5           | Input  | Time-division serial input enable                        | -         |

| TSIAK    | 83           | N5           | Output | Time-division serial input acknowledge                   | _         |

**Remark** Those pins marked "3S" in the above table enter the high-impedance state when data transmission is completed and when the hardware reset (RESET) signal is input.

# Host interface

| Pin Name       | Pin          | Pin No.                     |             | Function                                                                                                                                                                                                                                                                                                                                                                                    | Alternate                                                                                 |

|----------------|--------------|-----------------------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|

|                | 144-pin LQFP | 161-pin FBGA                |             |                                                                                                                                                                                                                                                                                                                                                                                             | Pin                                                                                       |

| HA1            | 63           | J3                          | Input       | <ul> <li>Host address 1</li> <li>This pin specifies a register that is accessed by the host interface pins (HD7 to HD0, or HD15 to HD0).</li> <li>1: The host interface status register (HST) is accessed.</li> <li>0: The host transmit data register (HDT (out)) is accessed for read (HRD = 0) and the host receive data register (HDT (in)) is accessed for write (HWR = 0).</li> </ul> | _                                                                                         |

| HAO            | 62           | К1                          | Input       | <ul> <li>Host address 0</li> <li>This pin specifies a register that is accessed by HD7 to HD0 in 8-bit mode. This pin is invalid in 16-bit mode.</li> <li>1: Bits 15 to 8 of HST, HDT (in), and HDT (out) are accessed.</li> <li>0: Bits 7 to 0 of HST, HDT (in), and HDT (out) are accessed.</li> </ul>                                                                                    | _                                                                                         |

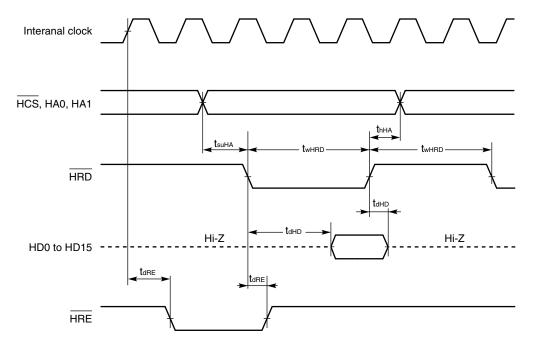

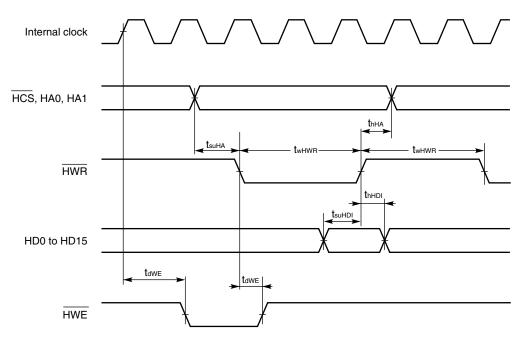

| HCS            | 61           | J2                          | Input       | Chip select input                                                                                                                                                                                                                                                                                                                                                                           | _                                                                                         |

| HRD            | 64           | К2                          | Input       | Host read input                                                                                                                                                                                                                                                                                                                                                                             | _                                                                                         |

| HWR            | 66           | J4                          | Input       | Host write input                                                                                                                                                                                                                                                                                                                                                                            | _                                                                                         |

| HRE            | 65           | L2                          | Output      | Host read enable output                                                                                                                                                                                                                                                                                                                                                                     | _                                                                                         |

| HWE            | 67           | L1                          | Output      | Host write enable output                                                                                                                                                                                                                                                                                                                                                                    | _                                                                                         |

| HD0 to<br>HD7  | 49 to 56     | F4,F2,F3,G1,<br>G3,G2,H3,H2 | I/O<br>(3S) | 8-bit host data bus<br>These pins constitute a host data bus in 8-bit host<br>mode. Access to 16-bit data for input/output is<br>controlled by the HA0 pin, and the data is accessed<br>two times such that it is divided into two blocks of 8-<br>bit data.<br>In 16-bit mode, the lower 8 bits of the data are<br>input/output.                                                           | _                                                                                         |

| HD8 to<br>HD15 | 39 to 46     | C2,C3,D1,D2,<br>D3,E3,E1,E2 | 1/O<br>(3S) | Host data bus<br>These pins constitute a host data bus in 16-bit host<br>mode. They input/output 16-bit data with HD0 to<br>HD7.                                                                                                                                                                                                                                                            | P8 to P15/<br>INT02,<br>INT12,<br>INT22,<br>INT32,<br>INT03,<br>INT13,<br>INT23,<br>INT33 |

**Remark** Those pins marked "3S" in the above table enter the high-impedance state while the host interface is not being accessed.

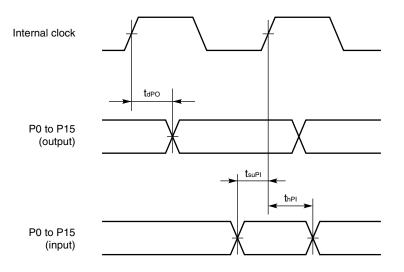

#### Pin Name Pin No. I/O Alternate Function Pin 144-pin LQFP 161-pin FBGA P0 28 C5 I/O General-purpose I/O port INT00 P1 29 D6 I/O INT10 A4 P2 30 INT20 I/O B5 P3 31 I/O INT30 P4 C4 32 I/O INT01 P5 33 INT11 A3 I/O P6 34 B4 I/O INT21 Ρ7 35 В3 I/O INT31 C2 INT02/HD8 P8 39 I/O P9 СЗ INT12/HD9 40 I/O P10 41 D1 INT22/HD10 I/O P11 INT32/HD11 42 D2 I/O P12 43 D3 INT03/HD12 I/O INT13/HD13 P13 44 E3 I/O P14 45 E1 I/O INT23/HD14 P15 46 E2 I/O INT33/HD15

# • I/O port

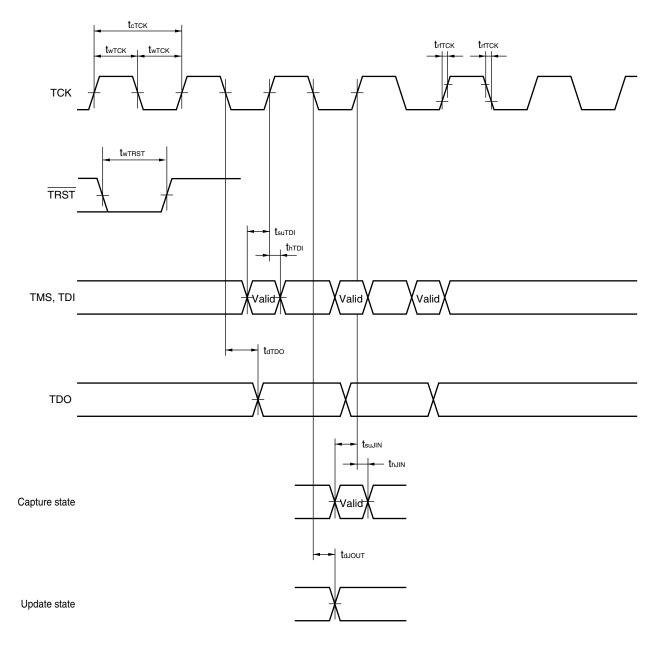

#### • Debugging interface

| Pin Name | Pin          | Pin No.      |                | Function                                                         | Alternate |

|----------|--------------|--------------|----------------|------------------------------------------------------------------|-----------|

|          | 144-pin LQFP | 161-pin FBGA |                |                                                                  | Pin       |

| TDO      | 141          | C12          | Output<br>(3S) | For debugging<br>This interface pins are used when a debugger is | -         |

| TICE     | 142          | D12          | Output         | used.                                                            | -         |

| тск      | 2            | B12          | Input          |                                                                  | _         |

| TDI      | 3            | C11          | Input          |                                                                  | _         |

| TMS      | 4            | D11          | Input          |                                                                  | _         |

| TRST     | 5            | A12          | Input          |                                                                  | _         |

**Remark** Those pins marked "3S" in the above table enter the high-impedance state while the debugging interface is not being accessed.

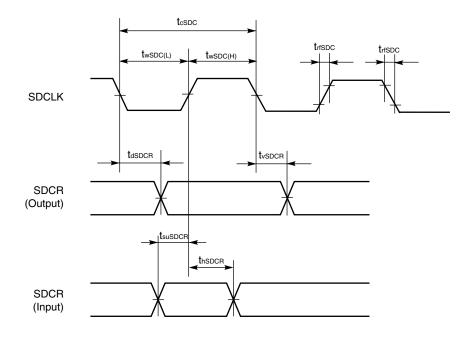

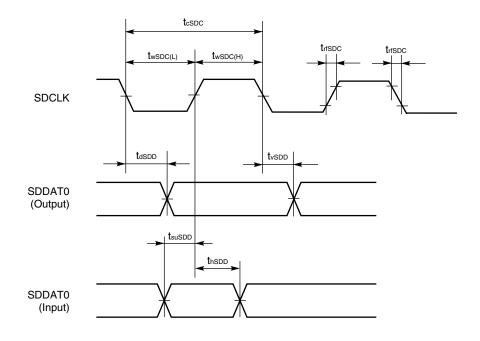

# •SD card interface (µPD77213 only)

| Pin Name | Pin No.      |               | I/O    | Function                                         | Alternate |

|----------|--------------|---------------|--------|--------------------------------------------------|-----------|

|          | 144-pin LQFP | 161-pin FBGA  |        |                                                  | Pin       |

| SDCLK    | 112          | M12           | Output | SD card clock output                             | MA19      |

|          |              |               |        | Leave this pin open.                             |           |

| SDCR     | 111          | M13           | I/O    | SD cord command/response                         | MA18      |

|          |              |               | (3S)   | Input: Response                                  |           |

|          |              |               |        | Output: Command                                  |           |

|          |              |               |        | • Leave pull-up.                                 |           |

| SDDAT0   | 104          | L10           | I/O    | SD card data input/output                        | MA14      |

|          |              |               | (3S)   | Input: Read data                                 |           |

|          |              |               |        | Output: Write data                               |           |

|          |              |               |        | Leave pull-up.                                   |           |

| SDMON    | 103          | P11           | Output | SD card interface access monitor                 | MA13      |

|          |              |               |        | This pin outputs a high level when the SD card   |           |

|          |              |               |        | interface is being accessed.                     |           |

|          |              |               |        | 1: SD card interface being accessed              |           |

|          |              |               |        | 0: SD card interface not being accessed          |           |

| Reserved | 105 to 107   | M11, N11, N12 | _      | Reserved for future function expansion.          | MA15 to   |

|          |              |               |        | This pin becomes high impedance when the SD card | MA17      |

|          |              |               |        | interface is being used.                         |           |

**Remark** Those pins marked "3S" in the above table enter the high-impedance state when the SD card interface is not being accessed.

# Others

| Pin Name | Pin          | Pin No.      |   | Function               | Alternate |

|----------|--------------|--------------|---|------------------------|-----------|

|          | 144-pin LQFP | 161-pin FBGA |   |                        | Pin       |

| I.C.     | 6, 7         | B11, C10     | - | Internally connected.  | -         |

|          |              |              |   | Leave these pins open. |           |

| NC       | _            | A1,A2,A13,   | - | No connection.         | -         |

|          |              | A14,B1,B2,   |   | Leave these pins open. |           |

|          |              | B13,B14,E5,  |   |                        |           |

|          |              | N1,N2,N13,   |   |                        |           |

|          |              | N14,P1,P2,   |   |                        |           |

|          |              | P13,P14      |   |                        |           |

Caution If any signal is input to these pins or if these pins are read, the correct operation of the  $\mu$ PD77210 Family is not guaranteed.

# 1.2 Connection of Unused Pins

# 1.2.1 Connection of functional pins

Connect the unused pins as shown in the table below.

| Pin Name                      | I/O    | Recommended Connection                                                                 |

|-------------------------------|--------|----------------------------------------------------------------------------------------|

| STOPS, HALTS                  | Output | Leave open.                                                                            |

| CSTOP                         | Input  | Connect to GND via a pull-down resistor.                                               |

| CLKOUT                        | Output | Leave open.                                                                            |

| P0 to P15                     | I/O    | Connect to EV <sub>DD</sub> via a pull-up resistor or to GND via a pull-down resistor. |

| HD0 to HD7 <sup>Note 1</sup>  | I/O    | Connect to EV <sub>DD</sub> via a pull-up resistor or to GND via a pull-down resistor. |

| HA0, HA1                      | Input  | Connect to EV <sub>DD</sub> via a pull-up resistor or to GND via a pull-down resistor. |

| HCS, HRD, HWR                 | Input  | Connect to EV <sub>DD</sub> via a pull-up resistor.                                    |

| HRE, HWE                      | Output | Leave open.                                                                            |

| TIMOUT                        | Output | Leave open.                                                                            |

| ASCK, TSCK                    | Input  | Connect to EV <sub>DD</sub> via a pull-up resistor or to GND via a pull-down resistor. |

| ASI, TSI                      | Input  |                                                                                        |

| ASIEN, TSIEN                  | Input  | Connect to GND via a pull-down resistor.                                               |

| ASOEN, TSOEN,                 | Input  |                                                                                        |

| LRCLK                         |        |                                                                                        |

| ASO, TSO                      | Output | Leave open.                                                                            |

| TSORQ                         | Output |                                                                                        |

| TSIAK                         | Output |                                                                                        |

| MA0 to MA19                   | Output | Leave open.                                                                            |

| MD0 to MD15 <sup>Note 2</sup> | I/O    | Connect to $EV_{DD}$ via a pull-up resistor or to GND via a pull-down resistor.        |

| MRD, MWR                      | Output | Leave open.                                                                            |

| MHOLDRQ                       | Input  | Connect to EVDD via a pull-up resistor.                                                |

| MBSTB, MHOLDAK                | Output | Leave open.                                                                            |

| MWAIT                         | Input  | Connect to EV <sub>DD</sub> via a pull-up resistor.                                    |

| ТСК                           | Input  | Connect to GND via a pull-down resistor.                                               |

| TDO, TICE                     | Output | Leave open.                                                                            |

| TMS, TDI                      | Input  | Leave open (this pin is internally pulled up).                                         |

| TRST                          | Input  | Leave open (this pin is internally pulled down).                                       |

**Notes 1.** These pins may left opened if the HCS, HRD,and HWR are fixed to the high level. However, connect these pins as recommended in the HALT and STOP modes when the power consumption must be lowered.

2. These pins may leave opened if the external data memory is not accessed in the program. However, connect these pins as recommended in the HALT and STOP modes when the power consumption must be lowered.

Caution Unused alternate-function pins should be handled in accordance with the processing specified for the pin function of the initial setting.

# 1.2.2 Connection of non-functional pin

| Pin name | I/O | Recommended Connection |

|----------|-----|------------------------|

| I.C.     | -   | Leave open.            |

| NC       | -   | Leave open.            |

# 2. FUNCTIONAL OUTLINE

# 2.1 Program Control Unit

This unit controls the execution of  $\mu$ PD77210 Family by executing instructions and controlling branching, loop, interrupts, clock, and standby mode.

# 2.1.1 CPU control

A three-stage pipeline architecture is employed so that all instructions, except branch instructions and some others, can be executed with one system clock.

#### 2.1.2 Interrupt control

The interrupt control circuit services the interrupt requests input to the interrupt controller by an external pin  $(\overline{INTmn})$  or internal peripherals (such as the serial interface, host interface, timer, and DMA controller). The interrupt of each interrupt source can be individually enabled or disabled. In addition, multiple interrupts are also supported.

#### 2.1.3 Loop control stack

A loop function without any hardware overhead is realized. A 4-level loop stack is provided to support multiple loops.

#### 2.1.4 PC stack

A 15-level PC stack that stacks the program counter supports multiple interrupts/subroutine calls.

#### 2.1.5 Clock control

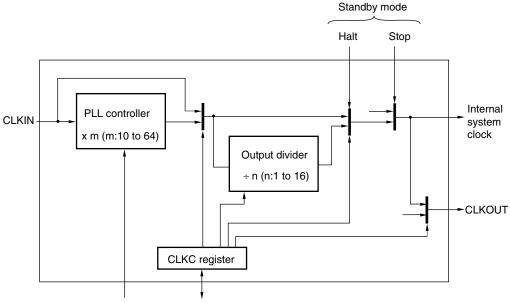

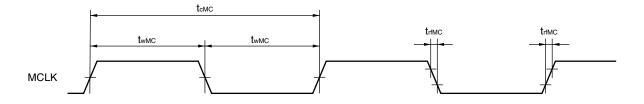

A PLL and a divider are internally provided as a clock generator so that an externally input clock is multiplied or divided and supplied as the operating clock to the  $\mu$ PD77210 Family. The multiple of the PLL can be set by using external pins (PLL0 to PLL3) within a range of ×10 to 64. The division ratio can be set by using a register in a range of ÷1 to 16.

The clock control register (CLKC) controls the power (ON/OFF) to the PLL, selects a clock source, controls the output divider, and controls the output of the CLKOUT pin.

Two types of standby modes are available so that the power consumption can be reduced when the  $\mu$ PD77210 Family is standing by.

•HALT mode: Current consumption falls to several mA upon execution of the HALT instruction.

This mode is released by an interrupt or hardware reset.

•STOP mode: Current consumption falls to hundreds of  $\mu A^{Note}$  upon execution of the STOP instruction.

This mode is released by hardware reset or inputting a signal to CSTOP pin.

Note When the PLL is stopped

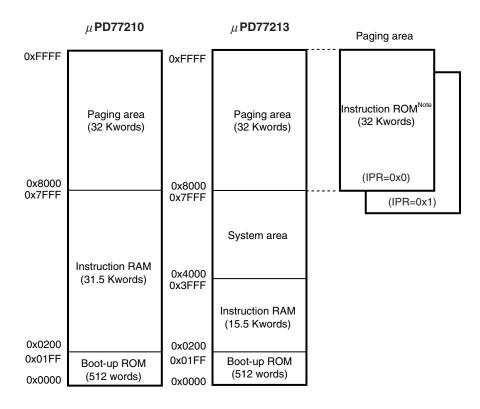

#### 2.1.6 Instruction memory

Of the instruction RAM, 64 words are allocated as interrupt vectors.

The  $\mu$ PD77210 is provided with an instruction RAM of 31.5 Kwords. The  $\mu$ PD77213 is provided with an instruction RAM of 15.5 Kwords and instruction ROM of 64 Kwords.

A boot-up ROM that boots up the instruction RAM is also provided, and the instruction RAM can be initialized or rewritten by means of a memory boot (booting from an internal or external data space), host boot (booting via a host interface), or serial boot (booting via a serial interface).

#### 2.2 Operation Unit

This unit performs multiplication, addition, logic, and shift operations, and consists of a 40-bit multiply accumulator, a 40-bit data ALU, a 40-bit barrel shifter, and eight 40-bit general-purpose registers.

#### 2.2.1 General-purpose registers (R0 to R7)

These eight 40-bit registers input/output operands and load/store data to/from data memory.

Each register consists of three parts: R0L to R7L (bits 15 to 0), R0H to R7H (bits 31 to 16), and R0E to R7E (bits 39 to 32). Depending on the type of the operation, RnL, RnH, and RnE are used either as one register or in combination.

#### 2.2.2 Multiply accumulator (MAC)

The multiply accumulator performs multiplication of two 16-bit data items and addition or subtraction between the result of the multiplication and one 40-bit data item, and then outputs 40-bit data.

A shifter (MSFT: MAC shifter) is provided at the preceding stage of the MAC, so that the 40-bit data that is to be added to or subtracted from the multiplication result can be arithmetically shifted 1 bit or 16 bits to the right before addition or subtraction.

#### 2.2.3 Arithmetic logic unit (ALU)

The ALU accepts one or two 40-bit data items as input, performs an arithmetic or logical operation, and then outputs 40-bit data.

#### 2.2.4 Barrel shifter (BSFT)

The BFST accepts 40-bit data items as input, shifts the data to the left or right by an arbitrary number of bits, and then outputs 40-bit data. The data can be shifted to the right arithmetically, in which case the sign of the data is extended, or logically in which case 0 is inserted starting from the MSB.

#### 2.3 Data Memory Unit

The data memory unit consists of two planes of data memory spaces and two pairs of data addressing units.

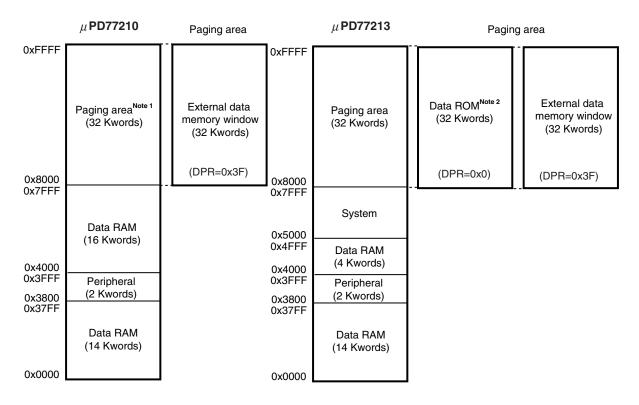

#### 2.3.1 Data memory

Two data memory planes (X data memory and Y data memory) are provided. The data memory space includes a 64-word peripheral area.

The  $\mu$ PD77210 has a data RAM consisting of 30 Kwords × 2 planes. The  $\mu$ PD77213 has a data RAM consisting of 18 Kwords × 2 planes, and has a data ROM consisting of 32 Kwords × 2 planes.

In addition, They also have an external data memory interface that is used to connect an external 1 Mword data memory to the device.

#### 2.3.2 Data addressing unit

An independent data addressing unit is provided for each of the X and Y data memory spaces.

Each data addressing unit has four data pointers (DPn), four index registers (DNn), one module register (DMX or DMY), and an address ALU.

#### 2.4 Peripheral Unit

The peripheral unit has serial interfaces, a host interface, general-purpose I/O ports, timers, an external memory interface, and SD card interface ( $\mu$ PD77213 only). All these internal peripherals are mapped to the X and Y data memory spaces and are accessed as memory-mapped I/Os by the program.

#### 2.4.1 Serial interface (SIO)

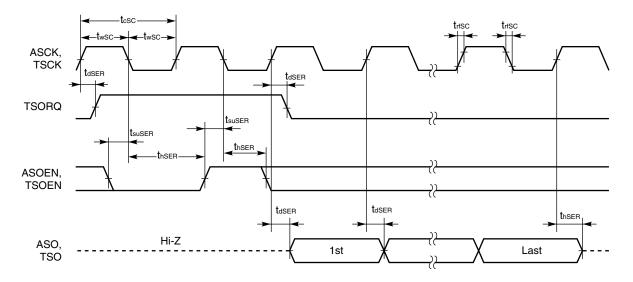

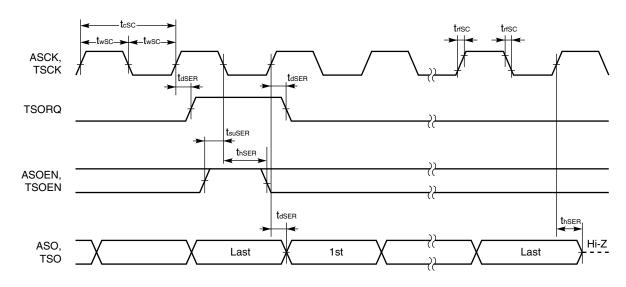

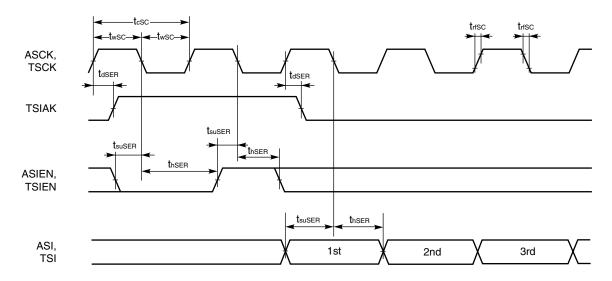

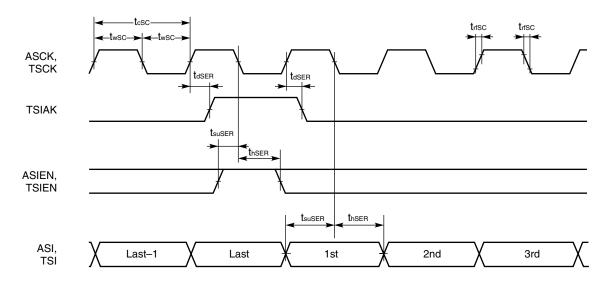

Two serial interface channels, an audio serial interface (ASIO) and a time-division serial interface (TDMSIO), are provided.

The audio serial interface can be used in either of two modes: audio mode and standard mode. The standard mode is compatible with the existing  $\mu$ PD77111 Family. The audio mode is compatible with the  $\mu$ PD77115.

The features of the audio mode are as follows:

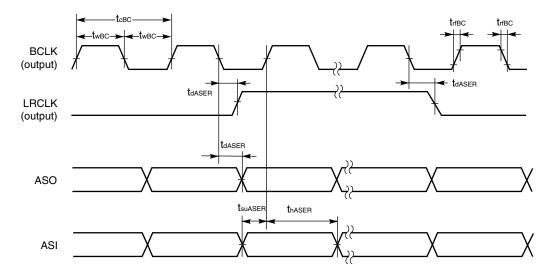

- Mode: Master mode and slave mode

- Master mode: Supports master clock input (MCLK), bit clock output (BCLK), LR clock output (LRCLK), 256 fs, 384 fs, and 512 fs.

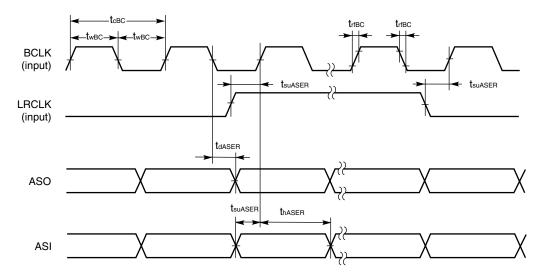

- Slave mode: Bit clock input (BCLK) and LR clock input (LRCLK)

- Frame format: 32- or 64-bit audio formats (LRCLK format)

- Handshake: Handshaking with external devices by a dedicated frame signal (LRCLK) and with the internal circuitry by polling, wait, or interrupt

The standard mode has the following features:

- •Serial clock: Supplied from an external source to each channel. The clock is shared for input and output by each channel.

- •Frame length: 8 or 16 bits, with MSB or LSB first selected for each channel.

- •Handshake: Handshaking with the external device by using a dedicated status signal and with the internal circuitry by polling, wait, or interrupt.

The time-division serial interface divides the serial input/output signal into 1 to 32 time slots and allows several devices to share the serial bus. Because the T1 and E1 frame signals are considered. The time slot can be extended from 1 to 128.

#### 2.4.2 Host interface (HIO)

This is a parallel port that inputs/outputs data from/to an external host CPU and DMA controller. It can be used in either 8-bit parallel mode or 16-bit parallel mode. In the  $\mu$ PD77210 Family, 16-bit registers are mapped to memory for input data, output data, and status. Handshaking with an external device is performed by using a dedicated status signal, and the internal circuitry handshaking is done by means of polling, wait, or interrupts.

The 8-bit parallel mode is compatible with the existing members of the  $\mu$ PD77111 Family.

In 16-bit parallel mode, some port pins are used as host interface pins.

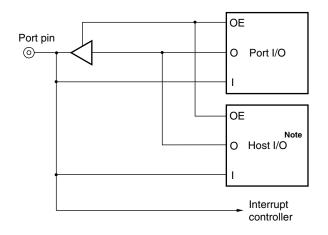

#### 2.4.3 General-purpose I/O port (PIO)

This is a 16-bit I/O port that can be set to either input or output mode in 1-bit units.

The external pins alternate between interrupt pins and host interface pins. By setting the mode of 8 bits of the port to host interface pin mode, the host interface can be set in the 16-bit parallel mode.

#### 2.4.4 External memory interface (MIO)

This interface accesses an external 1 Mwords data memory area in either of two modes: direct access and DMA access modes. In DMA access mode, access is made via a memory-mapped register.

In direct access mode, the data paging register (DPR) is set to 0x3F and a page area is accessed as an access window. An address of the external memory consists of 20 bits with the 8-bit value of the index register added as bits 12 to 19.

In DMA access mode, the address is automatically updated when a memory-mapped register is accessed. The address is updated in an increment addressing mode in which the address is simply incremented, or in twodimensional addressing mode in which an offset is added to each line length.

The number of wait cycles to be inserted when the external memory is accessed can be specified by a register (MWAIT), within a range of 1 to 15. In addition, wait cycles can also be inserted by using the MWAIT pin.

#### 2.4.5 Timers (TIM1 and TIM2)

The  $\mu$ PD77210 Family has two timer channels.

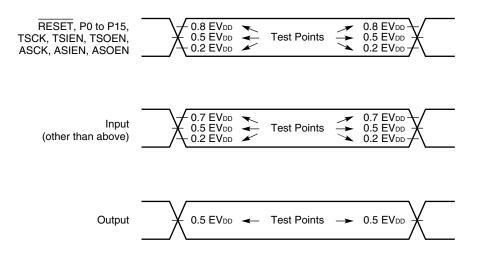

These timers can be used as interval timers, event counters, watchdog timers, and free-run timers.